Table Of Content

Verification can also take the form of comparing the implemented circuit to the original description to ensure it faithfully reflects the required function. Functional verification of a chip can also use simulation technology to compare actual behavior to expected behavior. These approaches are limited by the completeness of the input stimulus provided. Another approach is to verify the behavior of the circuit algorithmically, without the need for input stimulus.

Get the latest updates fromMIT Technology Review

The Chiplet architecture pioneered by AMD drives innovation in year on year improvements that feed compute heavy workloads. A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. For a more detailed exploration of this subject, we invite you to refer to our white paper titled A Survey of Machine Learning Applications in Functional Verification. In this white paper, we delve deeper into the topic, offering insights from an industrial perspective and discussing the pressing challenge posed by the limited availability of data. The full paper also includes exhaustive references to the fascinating research and writings that inform much of this article.

Electronic Design Automation for Next-Generation In-Memory Computing Systems - uat vcastapi

Electronic Design Automation for Next-Generation In-Memory Computing Systems.

Posted: Mon, 05 Feb 2024 08:00:00 GMT [source]

Embedded Systems Week

Besides manually defined test patterns, standard techniques employed in simulation-based verification include random test generation and graph-based intelligent testbench automation. Due to the “long tail” nature of coverage closure, even a tiny efficiency improvement can easily result in significantly reduced simulation time. Much research on the application of ML to functional verification has focused on this area. As a statistical method, ML cannot directly address formal verification problems. The Ada-boost decision tree-based classifier can improve the ratio of solved instances from the baseline orchestration from 95% to 97%, with an average speed up of 1.85.

Tessent Test and Embedded Analytics Solutions

Something rather significant happened during this time – the commercial application-specific integrated circuit, or ASIC, industry was also born. With the emergence of the ASIC industry, the custom chips that were previously reserved for the very large system OEMs were now within reach of many more design teams. With this new market, the need for tools to automate the simulation, design, and verification of chips became far more widespread. A lot of the internal, captive teams at the large OEMs found new, exciting, and lucrative work in this new market and so the commercial EDA industry began to grow.

Call for Nominations for Editor-in-Chief of the IEEE Embedded Systems Letters

It’s like the CAD software that architects use, except it’s more sophisticated, since it deals with billions of minuscule transistors on an integrated circuit. Design EDA tools take a proposed circuit function and assemble the elements needed to build it. Design EDA tools help teams create the right geometric shapes and give insight into how to connect these integral components. Often overseen by a designer, this process is also referred to as “place and route” or a custom layout. All of these elements can interact with each other in subtle ways, and variation in the manufacturing process can introduce more subtle interactions and changes in behavior.

The Importance of Electronic Design Automation in a Technology-Driven World

Even today, 8 of the top 10 systems (Green500 Nov/2023 rankings) are all based on AMD EPYC – a testament to our goals to make the most efficient compute engines. Here, we'd like to share how AMD IT uses our own technology to help advance our design engineers’ products. We refer to ourselves as “Customer Zero” - we experience the same challenges that our customer EDA IT environments face, and our internal IT solutions address the same problems. While that could very well be a possible author’s bias, this blog is not intended to highlight the technical excellence of our processors – that theme is effectively addressed by our Marketing and Engineering presentations/blogs/articles. Really interested to see how ML training models can free up verification time while better identify test to hit errors earlier in the process. ML might also help IC developers stay productive with semantic code search, which allows retrieving relevant code by NL queries.

What is China doing regarding EDA?

Leveraging IBM Cloud for electronic design automation (EDA) workloads - IBM

Leveraging IBM Cloud for electronic design automation (EDA) workloads.

Posted: Tue, 31 Oct 2023 07:00:00 GMT [source]

Widely used were the Espresso heuristic logic minimizer,[6] responsible for circuit complexity reductions and Magic,[7] a computer-aided design platform. Another crucial development was the formation of MOSIS,[8] a consortium of universities and fabricators that developed an inexpensive way to train student chip designers by producing real integrated circuits. The basic concept was to use reliable, low-cost, relatively low-technology IC processes and pack a large number of projects per wafer, with several copies of chips from each project remaining preserved.

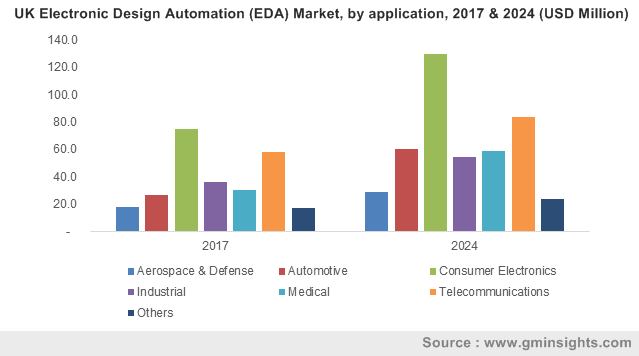

Overall, EDA tools are crucial in improving design efficiency, reducing time-to-market, enhancing design quality, and enabling the development of complex electronic systems. As designs have grown increasingly complicated, EDA software has become very important for developers involved in the production of printed circuit boards (PCB) and other circuit boards. If something goes wrong in the design process, electricity may not flow through the circuit correctly, rendering it dysfunctional.

Cable & Wire HarnessCreate, manage, and document your cable and wire harness assemblies in a comprehensive, integrated platform. Simulation & AnalysisTest and optimize before you build with our array of best-in-class simulation and virtual prototyping solutions. Synopsys helps you protect your bottom line by building trust in your software—at the speed your business demands.

The three primary companies leading this phase were Applicon, Calma, and Computervision. It is interesting to note that in these early days Calma developed a format to represent IC layouts called GDS, named after its product, Graphic Design System. The GDS II version of this format continued to be used as the de-facto format to communicate IC layout information for decades.

The specific procedure entails such steps as wiring, signal integrity analysis, parasitic parameter extraction, unit layout and optimisation, clock tree synthesis (CTS), layout physical planning, power analysis, and physical verification. While EDA solutions are not directly involved in the manufacture of chips, they play a critical role in three ways. First, EDA tools are used to design and validate the semiconductor manufacturing process to ensure it delivers the required performance and density.

Contrary to formal verification, simulation-based verification usually cannot ensure complete correctness in the design. Instead, the design is put under a test bench with certain random or fixed-pattern input stimuli applied, while the outputs are compared to the reference outputs to verify if the design’s behavior is expected. While simulation is the bread and butter of functional verification, simulation-based verification can also suffer from long verification times. It is not uncommon for the verification of a complex design to take weeks to complete. The implementation and flow of processes are mostly considered in the layout and simulation phases of the back-end design of digital circuits.

In our recent IP Lifecycle Management for Chiplet-Based SoCs webinar, Helix IPLM founder Simon Butler walks through best practices for managing IPs from inception through SoC integration. With traceability in mind, every aspect of the IP lifecycle is visible in Helix IPLM in easy-to-understand, configurable dashboards. Designers can see the projects the IP has been used in, any outstanding bugs, derivative designs, regression status, and much more.

No comments:

Post a Comment